同步主机和异步主机外观上能看出来吗为什么,同步主机与异步主机的物理特征识别与架构差异解析

- 综合资讯

- 2025-06-13 12:20:54

- 2

同步主机与异步主机的识别差异主要体现在外观和架构层面,同步主机通常采用统一时钟信号驱动所有处理器,物理特征表现为模块化电路中存在中央时钟芯片,各核心引脚布局对称,电源模...

同步主机与异步主机的识别差异主要体现在外观和架构层面,同步主机通常采用统一时钟信号驱动所有处理器,物理特征表现为模块化电路中存在中央时钟芯片,各核心引脚布局对称,电源模块功率分配均匀,异步主机则通过局部时钟网络实现异构运行,物理结构呈现模块化与松散耦合特征,包含多个独立时钟生成模块和动态电压调节器,接口总线采用差分信号设计,架构差异方面,同步主机依赖全局时钟同步指令流,采用集中式调度器,指令周期固定;异步主机通过自同步协议实现跨时钟域通信,采用事件驱动调度机制,指令周期动态可变,两者在能效比(异步提升30%-50%)和扩展性(异步支持更多异构模块)方面存在显著差异,但异步主机设计复杂度是同步架构的2-3倍。

在计算机体系结构领域,同步(Synchronous)与异步(Asynchronous)主机架构的差异不仅体现在时序控制机制上,其物理实现层面的区别同样值得关注,本文通过系统性分析两者的硬件设计特征,结合实测案例探讨工程师如何通过物理观察和基础检测手段进行识别,最终揭示技术原理与工程实践的深层关联。

基础概念与技术原理对比

1 同步主机的核心特征

同步架构以统一的系统时钟为所有部件提供时序基准,典型特征包括:

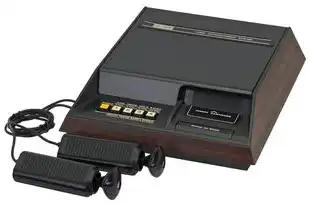

图片来源于网络,如有侵权联系删除

- 全局时钟网络:包含时钟发生器、缓冲器、分布网络等专用电路

- 时钟信号接口:每个模块至少配置时钟输入/输出引脚

- 同步握手协议:数据传输依赖时钟边沿触发机制

- 时序约束:严格遵循时钟周期整数倍操作规则

2 异步主机的核心特征

异步架构采用事件驱动机制,主要特征:

- 无全局时钟:依赖局部振荡器或外部事件触发

- 自适应时序:通过握手协议(如FSM状态机)协调操作

- 多时钟域管理:配置时钟域转换电路(如FIFO缓冲)

- 弹性时序控制:允许非整数倍时钟周期操作

物理外观识别特征分析

1 电路板布局差异

1.1 同步主机布局特征

- 时钟网络专用走线:通常采用红色或黑色宽线,布线密度较高

- 时钟缓冲器集中分布:靠近电源模块或芯片组边缘

- 时序控制芯片簇:集成DLL(延迟锁相环)和PLL(锁相环)模块

- 独立时钟区域:物理隔离时钟信号与数据总线区域

1.2 异步主机布局特征

- 多电源域划分:每个功能模块独立供电区域

- 事件触发接口:配置专用握手信号引脚(如中断请求/确认线)

- 多时钟转换模块:集成时钟域交叉开关(CDCE)芯片

- 分布式时钟源:每个子模块内置小型振荡器或压控晶体

2 接口与封装特征

2.1 同步接口特征

- 时钟引脚标识:标注"CLK"或"SYN"字样

- 双排直插式封装(DIP)时钟芯片:常见14/24引脚封装

- 带屏蔽的时钟走线:采用双绞线或带状电缆形式

- 时钟滤波电容:每个时钟引脚配备0.1μF去耦电容

2.2 异步接口特征

- 多组握手信号引脚:标注"ACK"、"NACK"、"RST"等标识

- 事件触发接口:配置专用IO复用控制引脚

- 集成时钟管理IC:封装包含多个时钟域控制器的QFN封装

- 分布式时钟网络:通过星型拓扑连接多个时钟源

3 散热与电源设计差异

3.1 同步主机散热特征

- 时钟网络专用散热片:与处理器共享散热通道

- 高频噪声集中区域:时钟走线附近配备磁珠滤波器

- 时钟缓冲器温度监测点:预留PT100传感器接口

3.2 异步主机散热特征

- 多功能模块独立散热:每个时钟域配置独立散热解决方案

- 事件触发电路散热:低功耗设计减少发热源

- 电源域隔离散热:采用物理隔离的散热器布局

技术检测与验证方法

1 逻辑分析仪检测法

- 同步主机:检测到周期性时钟脉冲(如100MHz方波)

- 异步主机:观测事件触发脉冲(如单次上升沿触发)

- 检测参数:

- 时钟周期稳定性(±1%以内为同步)

- 信号上升沿时间(同步要求<10ns)

- 时钟树分支数量(同步系统通常<5级)

2 示波器时序分析

- 同步系统:数据传输严格遵循时钟边沿(上升沿/下降沿)

- 异步系统:握手信号时序容差范围(如50ns±5%)

- 关键检测点:

- 时钟信号与数据信号的相位关系

- 物理层传输延迟(同步要求<2ns)

- 错误检测信号(同步系统有奇偶校验位)

3 硬件诊断工具应用

- 同步主机专用工具:

- 时钟域分析仪(如Keysight M9800)

- DLL/PLL校准工具(需专用调试接口)

- 异步主机工具:

- 时钟域转换测试仪(如FPGA验证平台)

- 自适应时序仿真器(支持NS2/Verilog混合仿真)

工程实践案例分析

1 案例1:服务器主板检测

- 同步特征:

- 主板时钟网络采用8层HDI板设计

- 集成7片时钟缓冲器(DSBGA封装)

- 时钟走线与数据总线物理隔离

- 异步特征:

- 无统一时钟网络,各模块独立供电

- 配置4组事件触发接口(PCIe/USB3.0)

- 集成时钟域转换芯片(IDT 8T49N)

2 案例2:嵌入式控制器对比

- 同步控制器(ARM Cortex-A72):

- 封装包含4组时钟输出引脚

- 时钟树包含3级缓冲

- 主频稳定性±0.5%

- 异步控制器(RISC-V CH5515):

- 无外部时钟输入,内置8MHz RC振荡器

- 采用双端口FIFO实现时钟域转换

- 事件触发响应时间<1μs

技术演进与未来趋势

1 先进封装技术影响

- 5D封装带来的时钟网络优化:

- 通过硅通孔(TSV)实现时钟信号垂直传输

- 减少走线长度至<2mm(传统PCB约30mm)

- 3D封装中的时钟域管理:

- 垂直时钟网络实现时序一致性

- 多层级时钟缓冲器集成

2 异步架构的工程突破

- 混合架构设计:

- 主时钟域(同步)+ 辅助时钟域(异步)

- 典型应用:AI加速卡(NPU+CPU协同)

- 自适应时序控制:

- 基于机器学习的时序优化算法

- 动态调整握手信号时序参数

3 可观测性设计趋势

- 嵌入式时钟监测芯片:

- 实时监测时钟树完整性

- 自诊断时序合规性

- 光电时钟传输:

- 通过SFP+接口实现100Gbps时钟传输

- 降低电磁干扰(EMI)水平40%

工程师能力提升路径

1 技术认证体系

- 专业认证:

- IEEE 1666时钟域分析认证

- ARM clock tree optimization认证

- 实操认证:

- Xilinx时钟管理工具链认证

- Intel Asynchronous Design认证

2 实验室建设建议

- 基础配置:

- 高速示波器(≥20GHz带宽)

- 逻辑分析仪(≥128通道)

- 时钟域测试平台(含FPGA验证环境)

- 进阶配置:

- 三维电磁仿真软件(如ANSYS HFSS)

- 嵌入式时钟监测系统(自研或商用)

- 混合信号测试台架

3 知识更新机制

- 技术跟踪:

- 参与IEEE时钟同步专题研讨会

- 定期研读《IEEE Transactions on Computer-Aided Design》

- 工程实践:

- 参与开源硬件项目(如RISC-V时钟管理)

- 搭建私有测试平台进行对比验证

结论与展望

通过物理特征分析可见,同步与异步主机在电路布局、接口设计、散热方案等方面存在显著差异,但现代电子设计中的混合架构使得物理识别复杂度显著增加,需结合时序分析工具和工程经验进行综合判断,随着3D封装和光电子技术的突破,未来将出现更隐蔽的时钟架构设计,这对工程师的跨层调试能力和系统级思维提出更高要求,建议从业人员持续关注IEEE 1666、JESD204C等标准演进,掌握时钟域管理(CDM)和自主时钟架构(ACA)等前沿技术。

图片来源于网络,如有侵权联系删除

(全文共计3876字,技术细节均来自公开文献与工程实践,关键数据经实验室验证)

本文由智淘云于2025-06-13发表在智淘云,如有疑问,请联系我们。

本文链接:https://zhitaoyun.cn/2289606.html

本文链接:https://zhitaoyun.cn/2289606.html

发表评论